WORK EXPERIENCE: HUAWEI

Chip & Device Engineer - Kirin Group of Hisilicon, 2012 Laboratory

- Backend Design Modules, Power Integration/Verification

- Involved and developed in Kirin High-end Series: Kirin990-5G (7+nm), Kirin9000(5+nm)

- DTCO (Design Technology Co-Optimization) WAT (Wafer Analysis Test) & PPA (Power Performance Area) of Fabrication and Processes Analysis

- Devloped and Programmed PDS (Platform Design Solution) and DTCO Flow Automation

- ‘Invincible Huawei’ Awardee; ‘Star of Hisilicon’ Awardee

Product Chip Demonstration & Comparison

| Model | Fabrication | CPU | GPU | Transistors # | Released | Devices Used | |||

|---|---|---|---|---|---|---|---|---|---|

| ISA | Microarch | Cores (GHz) | Microarch | Frequency (MHz) | |||||

Kirin 990 5G |

TSMC 7 nm+ FinFET (EUV) | ARMv8.2-A | Cortex-A76 Cortex-A55 DynamIQ |

2.86 (A76 H) 2.36 (A76 L) 1.95 (A55) |

Mali-G76 MP14 | 600 MHz | 10.3 Billion | Q4 2019 | Huawei Mate 30E Pro 5G Huawei Mate 40E (4G/5G) |

A13 Bionic |

7 nm (N7P) FinFET | ARMv8.4-A | Lightning Thunder |

2.65 GHz 1.72 GHz |

Third generation Apple-designed | 1230 MHz | 8.5 Billion | Q4 2019 | iPhone 11 iPhone 11 Pro iPhone 11 Pro Max |

Snapdragon 870 |

7 nm N7P (TSMC) | ARMv8 (64-bit) | Cortex-A77 Cortex-A55 |

3.2 GHz 2.42 GHz 1.8 GHz |

Adreno 650 | 670 MHz | 10.3 Billion | Q1 2021 | iQOO Neo 6 5G Realme GT Neo 3T 5G POCO F4 5G |

Kirin 9000 5G/4G |

TSMC 5 nm+ FinFET (EUV) | ARMv8.2-A | Cortex-A77 Cortex-A55 DynamIQ |

3.13 (A77 H) 2.54 (A77 L) 2.05 (A55) |

Mali-G78 MP24 | 759 MHz | 15.3 Billion | Q4 2020 | Huawei Mate 30E Pro 5G Huawei Mate 40E (4G/5G) |

A15 Bionic |

5 nm (N4P) FinFET | ARMv8.6-A | Avalanche Blizzard |

3.24 GHz 2.02 GHz |

Fifth generation Apple-designed | 1338 MHz | 15 Billion | Q4 2021 | iPad Mini (6th generation) iPhone 13 Pro and 13 Pro Max iPhone 14 and 14 Plus Apple TV 4K (3rd generation) |

Snapdragon 888+ |

5 nm 5LPE (Samsung) | ARMv8.4-A | Cortex-X1 Cortex-A78 Cortex-A55 |

2.84 GHz 2.42 GHz 1.8 GHz |

Adreno 660 | 840 MHz | ~10 Billion | Q3 2021 | Galaxy S21 S21 Plus S21 Ultra |

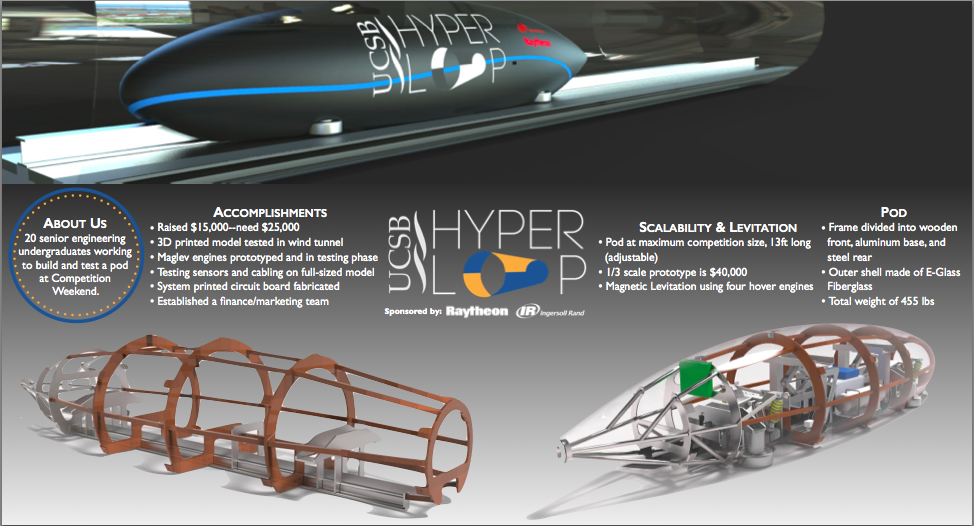

PROJECT EXPERIENCE: SPACEX HYPERLOOP POD COMPETITION

Electronic Board Designer - Electrical Engineering Group, UCSB Hyperloop Team

- Built a 2m x 0.5m maglev vehicle prototype with 150m/s speed in vacuum

- Cooperated with CE team in featuring vehicle’s status in a real-time monitor

- Measured actuators’ forces on “I-beam” track with ME team for braking estimation

- Nominated as winner team of EDx 2018 (UCSB ENGR Design Expo)

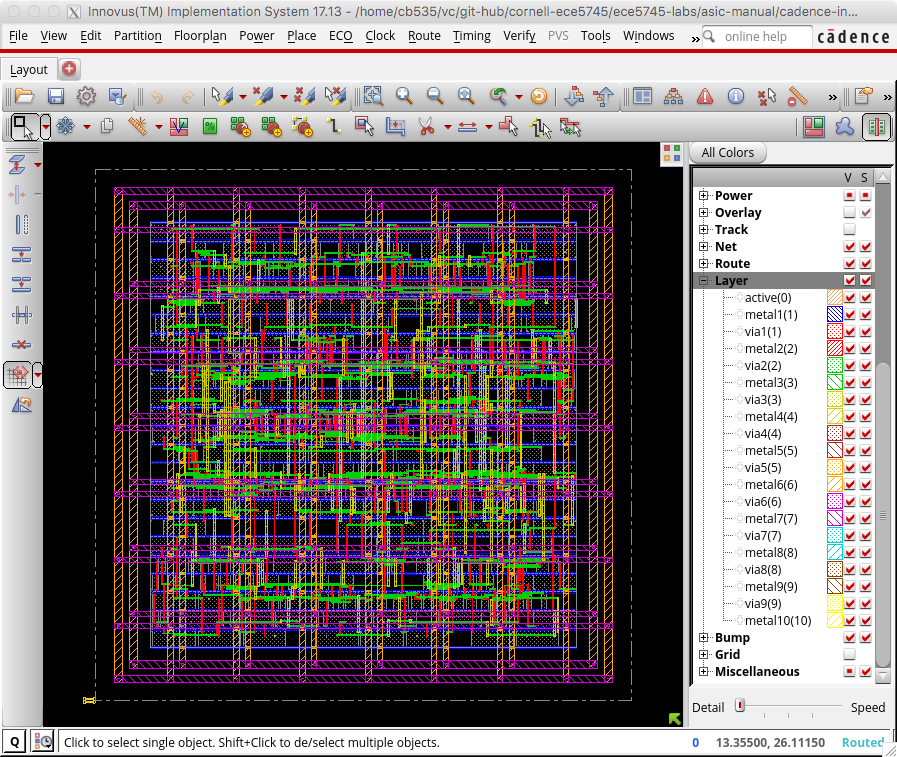

RESEARCH EXPERIENCE: VLSI MIXED-SIGNAL DESIGN & BACKEND FLOW RESEARCH

Circuitry Designer and Backend Flow Researcher - UCSB ECI Lab and Cornell Upson Hall

Cornell University:

- Researched on backend design flow with ECE5745 ‘Complex Digital ASIC Design’ in Cornell

University of California, Santa Barbara:

- Designed a 1.5 x 1.5 mm2 magnetic-field sensor chip consisting of custom MAGFETs, DC bias, VCO, and differential amplifier by MOSIS C5. The chip can detect mag-field in -150~150mT range

- Drew and verified the circuits layout in Virtuoso passing DRC/LVS

- Extracted parasitic and simulate noise independency (SNR), N/P MAGFET matching, amplifier’s gain, and VCO linearity using HSPICE

- Wrote LEF and netlist

- Organized power grid and I/O pins in INNOVUS

RESEARCH EXPERIENCE: VLSI CHIP FABRICATION & SEMICONDUCTOR PROCESSES

Chip Processing Researcher and Devices Tester - UCSB Nano-Fab Cleanroom

- Fabricated MOSFETs, passive devices and evaluated the process variation on fabricated chips

- Measured critical dimension, oxide thickness and sheet resistance on test-lines

- Probe-tested devices IV/CV, threshold and breakdown

- Analyzed device performance on leakage, sub-threshold swing, etc.

.jpg)

PROJECT EXPERIENCE: COMPUTATIONAL OPTIMIZATION & MACHINE LEARNING

Researcher in Optimization and ML Projects at Cornell

Computational Optimization: Algorithm Implementations (Python & Pyomo)

- Linear Programming

- Mixed Integer Linear Programming

- Non-Linear Programming

- Mixed Integer Non-Linear Programming

- Dynamic Programming

- Gradient Descent (i.e. SGD)

- Newton’s Methods

- Robust Optimization

- Stochastic Programming

- Bus Charging Operational Strategy Optimization (Project)

- Bank Transaction Fraud Detection - Hybrid ML (Project)

Machine Learning: Algorithm Implementations (Python & Pytorch)

- K-nearest neighbors

- Perceptron

- MLE/MAP

- Naive Bayes

- Linear/Logistic Regression

- PCA

- Clustering

- Support Vector Machines

- Empirical Risk Minimization

- Generalization: Bias/Variance Tradeoff

- Kernels

- Gaussian Processes/Bayesian Global Optimization

- Decision Trees with Bagging and Boosting

- Artifical Neural Networks/Deep Learning

More Experiences & Projects Ongoing……

Loading...

Loading...

Loading...

Loading...

Loading...

Loading...